Design with

Multi-Gigabit Serial I/O Design with

Multi-Gigabit Serial I/O |

|

|

|

|

| |

|

|

|

Description

MVD Cores develops communication

protocols for any proprietary high speed

link including:

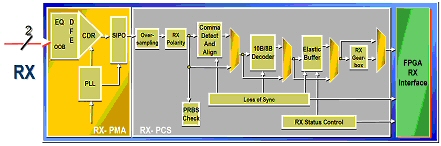

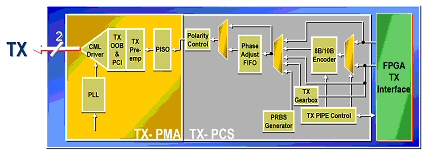

- Clock Configuration

- Clock/Data recovery

- Parallel/Serial, Serial/Parallel

conversion

- Byte/Word alignment

- Channel Bonding

- Clock Correction

- Encoder/Decoder

- PRBS generator/checker

- Termination, Equalizer and

Polarity Control

|

|

|

|

|

|

|

Available technology

| Device |

Family |

Transceiver

type |

Serial

transceiver

Max achievable rate

(Gb/s) |

Max

number of

transceivers

per single device |

| Spartan-6™ |

LXT |

GTP |

3.125 |

8 |

| Virtex-6™ |

LXT/SXT |

GTX |

6.6 |

36 |

| Virtex-6™ |

HXT |

GTX |

6.6 |

48 |

| Virtex-6™ |

HXT |

GTH |

11.1 |

24 |

| Artix-7™ |

All |

GTP |

3.75 |

16 |

| Kintex-7™ |

All |

GTX |

12.5 |

32 |

| Virtex-7™ |

V and XC7VX485T™ |

GTX |

12.5 |

36

or 56 |

| Virtex-7™ |

VX (except

XC7VX485T™) |

GTH |

13.1 |

96 |

| Virtex-7™ |

VH |

GTH |

13.1 |

72 |

| Virtex-7™ |

VH |

GTZ |

28.5 |

76 |

|

|

High-speed Serial Applications

- Chip-to-chip

- Computing

- Datacom

- Storage

- Telecom

- Video

|

|

|

|

|

|