Conception avec les

transceivers Multi-Gigabit Conception avec les

transceivers Multi-Gigabit |

|

|

|

|

| |

|

|

|

Description

MVD Cores développe des protocoles de

communication pour toute liaison haute

vitesse propriétaire incluant :

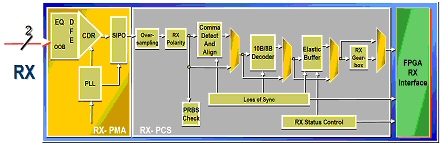

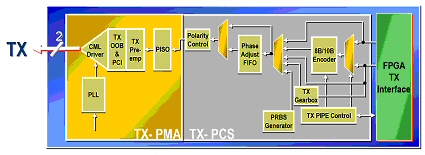

- Configuration d'horloge

- Récupération horloge/donnée

- Conversion parallèle/série, série/parallèle

- Alignment Byte/Word

- Channel Bonding

- Correction d'horloge

- Encodeur/decodeur

- Génération/véricifation PRBS

- Terminaison, égaliseur et controle

de polarité

|

|

|

|

|

|

|

Technologie disponible

| Composant |

Famille |

Type

de transceiver

|

Débit

max atteignable

par le transceiver série

(Gb/s) |

Nombre

maximum

de transceivers

par composant |

| Spartan-6™ |

LXT |

GTP |

3.125 |

8 |

| Virtex-6™ |

LXT/SXT |

GTX |

6.6 |

36 |

| Virtex-6™ |

HXT |

GTX |

6.6 |

48 |

| Virtex-6™ |

HXT |

GTH |

11.1 |

24 |

| Artix-7™ |

All |

GTP |

3.75 |

16 |

| Kintex-7™ |

All |

GTX |

12.5 |

32 |

| Virtex-7™ |

V et

XC7VX485T™ |

GTX |

12.5 |

36

or 56 |

| Virtex-7™ |

VX (excepté

XC7VX485T™) |

GTH |

13.1 |

96 |

| Virtex-7™ |

VH |

GTH |

13.1 |

72 |

| Virtex-7™ |

VH |

GTZ |

28.5 |

76 |

|

|

Applications série haute vitesse

- Chip-to-chip

- Calcul

- Datacom

- Stockage

- Telecom

- Video

|

|

|

|

|

|